本白皮书重点介绍 Wolfspeed 专为高功率电子应用而设计的第 4 代碳化硅 (SiC) MOSFET 技术。基于在碳化硅创新领域的传承,Wolfspeed 定期推出尖端技术解决方案,重新定义行业基准。在第 4 代发布之前,第 3 代碳化硅 MOSFET 凭借多项重要设计要素的平衡,已在广泛用例中得到验证,为硬开关应用的全面性能设定了基准。

第 4 代 MOSFET 主要面向高功率汽车、工业和可再生能源系统,为碳化硅技术带来了新的范式。此类器件为产品开发的长期路线图提供了灵活的基础,包括应用优化的裸芯片、模块和分立式产品等。基于第 4 代技术的每项设计都关注三个性能向量:整体系统效率;卓越的耐久性;较低系统成本。所有这些特性都旨在助力设计人员实现前所未有的性能和价值。

性能效率提升

导通损耗的重要性

第 3 代 MOSFET 与第 4 代 MOSFET 性能对比

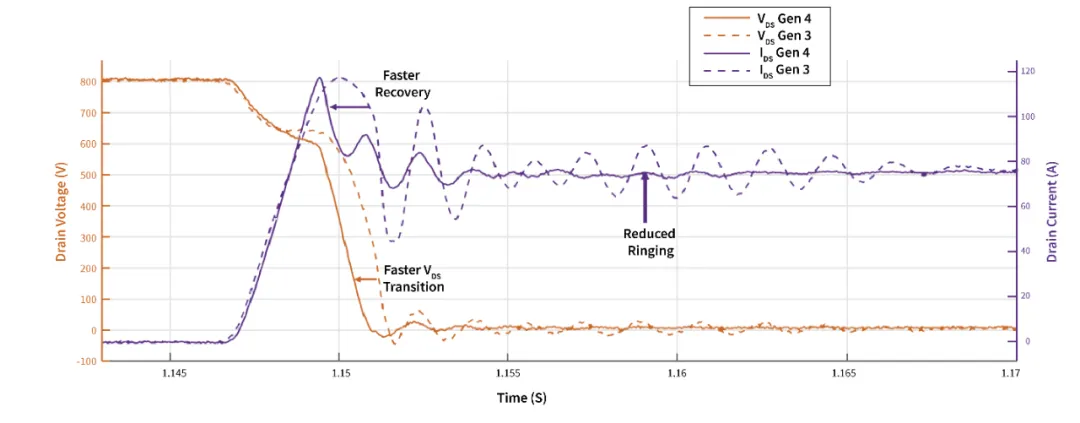

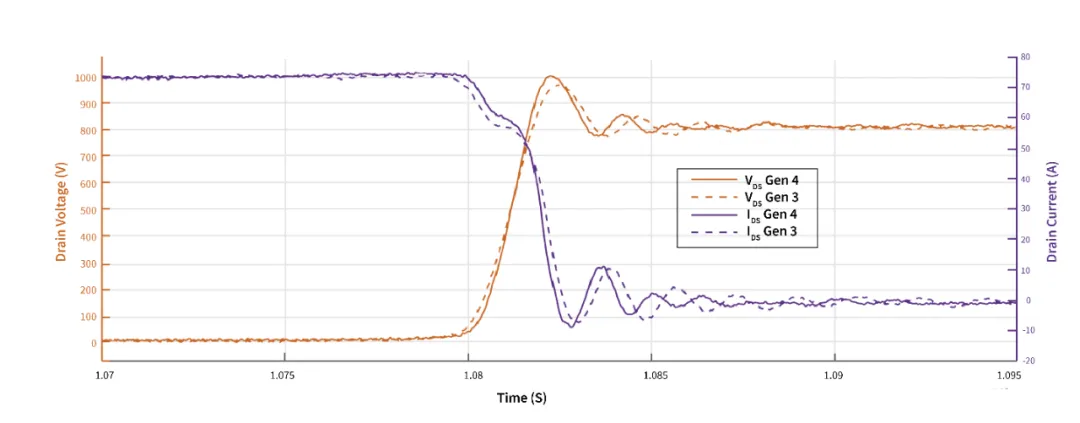

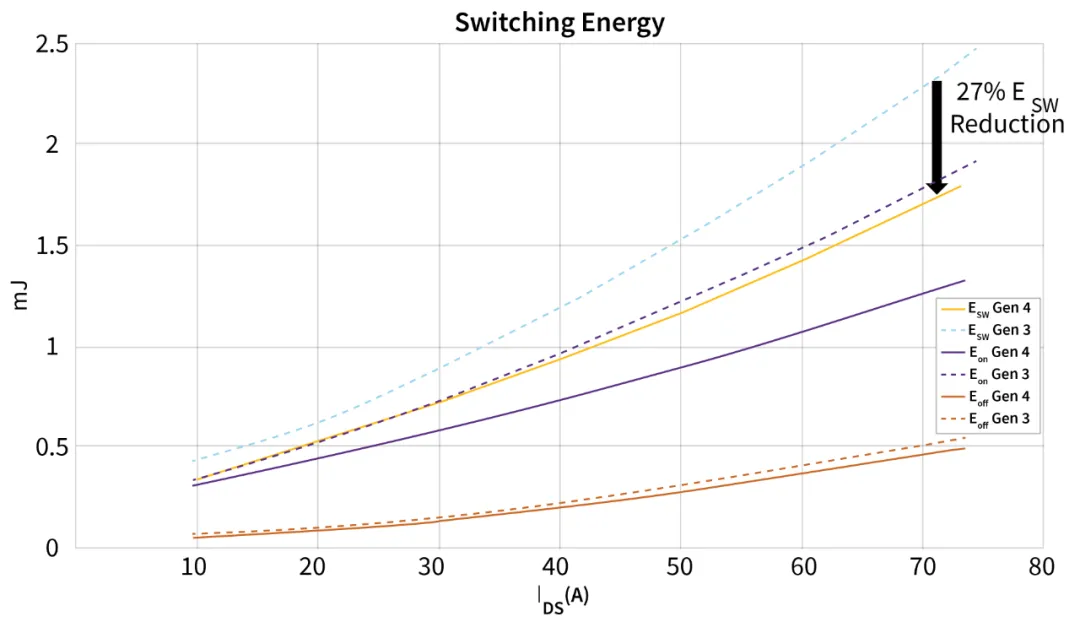

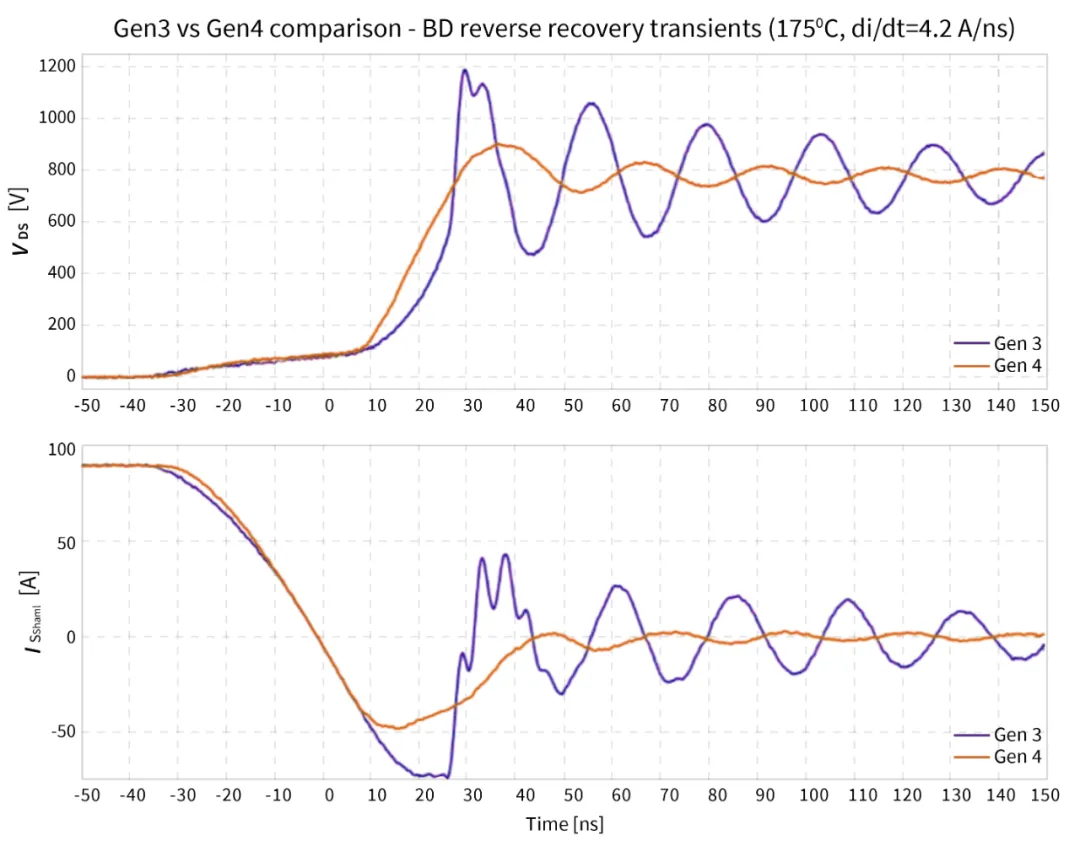

为了说明第 4 代 MOSFET 在开关损耗和易用性方面的改进,应考虑半桥开关事件的波形。在第 3 代器件所具有的出色性能和可靠性基础上,Wolfspeed 第 4 代 MOSFET 通过改进提高了开关速度并减少了电压过冲,这得益于体二极管性能的提升和设计的优化。第 4 代器件的这些改进建立在第 3 代的强大基础之上,确保了在产品组合过渡期间,即便是在要求严苛的应用中,也能保持一贯的卓越表现。

图 2 和图 3 显示了 1200 V 第 4 代器件与第 3 代等效器件在动态开关性能方面的对比。调整栅极电阻值,以便在导通期间提供匹配的 di/dt,在关断期间提供匹配的 dv/dt。第 4 代器件能够实现更快的开关速度,这里仅展示了一种比较器件性能的保守方法。

图 2:第 3 代和第 4 代 MOSFET 的导通波形对比

改进的体二极管性能以及由此提升的开通性能可大幅降低第 4 代器件的开关损耗。在许多情况下,开关损耗的降低幅度甚至更大,因为第 4 代器件可在更高的 di/dt 水平下工作,同时在反向恢复过程中不会超出 VDS 安全工作区。

从图 2 的对比中可以看出,第 4 代 MOSFET 的另一个优势在于减少了反向恢复后的振荡和振铃。与第 3 代相比,第 4 代 MOSFET 的波形更为平滑,最大限度地减少了共模电压和辐射发射,简化了电磁干扰 (EMI) 滤波器设计。

* 进一步了解实现 EMI 合规性的设计捷径。

高海拔应用(如在山区行驶的电动汽车或飞机)会面临由宇宙射线引发的单粒子烧毁风险。这些事件由中子通量(每单位时间撞击半导体的中子数)引起,可产生漏源电流 (IDS),进而可能引发不良后果。

软开关应用的主要优势在于减少因 RSP 改进而降低的导通损耗。这种导通损耗的降低适用于整个负载曲线,对于有能效要求(如能源之星 Energy Star 标准)的应用尤其有益。其中许多电源必须符合要求在不同负载水平下实现高效率的法规,例如,满足服务器电源的 80 Plus 钛金级能效水平。

系统成本和开发时间优势

优化功率封装以充分发挥第 4 代技术的优势

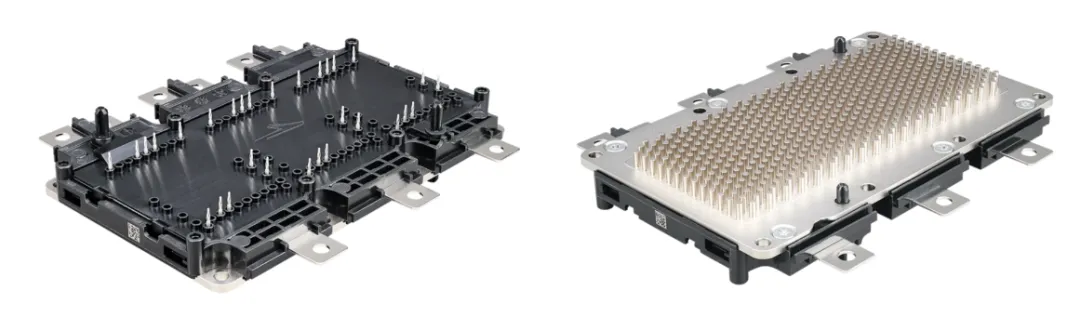

Wolfspeed 始终关注客户需求,致力于通过封装策略实现系统耐久性、效率和功率密度。先进的封装进一步提升了第 4 代技术的优势,增强了热管理,并确保了器件在功率和温度循环等严苛条件下的耐久性。

可显著提升效率和功率密度的先进封装

专为碳化硅量身定制的先进封装技术可最大限度地减少功率、栅极和共源回路中的寄生电感,从而提高效率,降低开关损耗,并支持使用额定值更低的碳化硅器件。双面冷却和紧凑布局等功能支持高功率应用、热控制和更高的开关频率,从而充分发挥碳化硅在可靠且节能系统中的潜力。

最大限度地减少功率模块中的电感可以减少电压振荡,实现简洁的开关操作和更高的效率。内部母线和夹子附件等创新技术将电感降低至 5 纳亨的水平,进一步降低了开关损耗并提升了系统稳定性。

图 6:Wolfspeed 的 YM 和 XM 模块平台

采用 pin-fin 封装技术

关键要点和结论

本译文仅供参考,只有英文原稿才可以被视为权威资料来源。