IP核

基于XADC IP核的FPGA芯片温度读取设计

本文利用VerilogHDL语言,通过Xilinx提供的XDAC IP核实现ZYNC-7000 SOC芯片温度实时读取。

智能无人设备从IP核到系统的全流程功能安全问题初探

为了确保智能化和无人化设备的安全可控,设计师在进行系统开发的时候,就必须重视从流程的第一步和最底层的技术源头考虑功能安全问题。

了解汽车与航空电子等安全关键型应用的IP核考量因素

本文的目的是阐明在安全关键型应用中使用预先打造的电路功能(也就是IP内核)的益处,并为您在设计芯片时,在做出相关选择和IP内核集成过程中提供一些指导。

使用 Vitis Model Composer 生成 FPGA IP 核

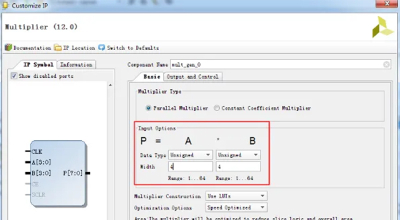

今天的教程提供了创建自定义 IP 的分步指南,从算法开发到准备 IP 生成的模型,包括资源和时序分析,最后将其添加到 Vivado IP 目录。

分页

- 页面 1

- 下一页