PCB

PCB的板级去耦设计方法和实例讲解

一,什么是PCB中的板级去耦呢?

板级去耦其实就是电源平面和地平面之间形成的等效电容,这些等效电容起到了去耦的作用。主要在多层板中会用到这种设计方法,因为多层板可以构造出电源层和地层,而一层板与两层板没有电源层和地层,所以设计不了板级去耦。

二,如何设计板级去耦?

多层板pcb在设计板级去耦时,为了达到最好的板级去耦效果,一般在做叠层设计时把电源层和地层设计成相邻的层。相邻的层降低了电源、地平面的分布阻抗。从平板电容的角度来分析,由电容计算公式C=εs/(4πkd)可以,两平板之间的距离d越小,电容值越大,相当于加了一个大的电解电容,相邻的层两平面的d是最小的,所以电源层和地层设计成相邻的层,可以达到最好的去耦效果。

三,实例分析

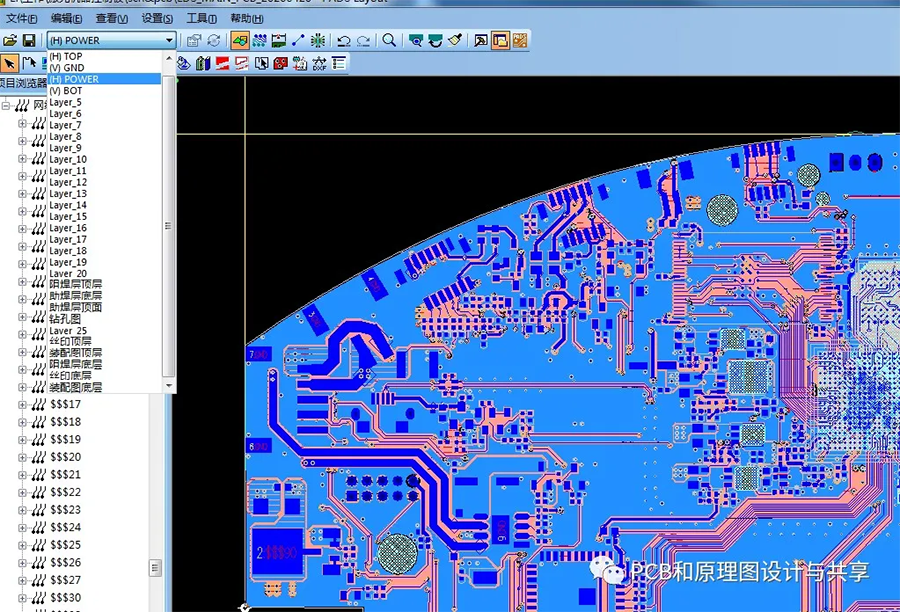

1.设计四层板时,中间两层分别是电源板和地层

电源层做了很多个电源平面的分割,

警惕!CAF效应导致PCB漏电~

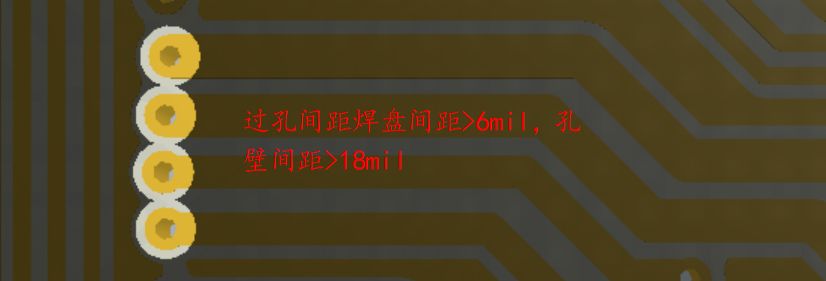

最近碰到一个PCB漏电的问题,起因是一款低功耗产品,本来整机uA级别的电流,常温老化使用了一段时间后发现其功耗上升,个别样机功耗甚至达到了mA级别。仔细排除了元器件问题,最终发现了一个5V电压点,在产品休眠的状态下本该为0V,然而其竟然有1.8V左右的压降!耐心地切割PCB线路,惊讶地发现PCB上的两个毫无电气连接的过孔竟然可以测试到相互间几百欧姆的阻值。查看该设计原稿,两层板,过孔间距焊盘间距>6mil,孔壁间距>18mil,这样的设计在PCB行业中实属普通的钻孔工艺。洗去油墨,排除油墨或孔表层的杂质导电问题,实测过孔间阻值依然存在!百思不得其解一段时间后,才发现原来是“CAF效应”导致的漏电问题!

什么是CAF效应:

CAF,全称为导电性阳极丝(CAF:Conductive Anodic Filamentation), 指的是PCB内部铜离子从阳极(高电压)沿着玻纤丝间的微裂通道,向阴极(低电压)迁移过程中发生的铜与铜盐的漏电行为。

工程师必备:硬件EMC设计规范

一、引言

广义的电磁兼容控制技术包括抑制干扰源的发射和提高干扰接收器的敏感度,我们都知道干扰源、干扰传输途径和干扰接收器是电磁干扰的三要素,同时EMC也是围绕这些问题进行研究,而运用最为广泛的抑制方法是屏蔽、滤波和接地,用它们来切断干扰的传输途径。

本文将着重在单板的EMC设计上,介绍一些重要的EMC知识及法则。在最初电路板的设计阶段就着手考虑对电磁兼容的设计,种类包括公共阻抗耦合、串扰、高频载流导线产生的辐射和通过由互连布线和印制线形成的回路噪声等。

在高速逻辑电路里,这类问题特别脆弱,原因很多:

(1)电源与地线的阻抗随频率增加而增加,公共阻抗耦合的发生比较频繁;

(2)信号频率较高,通过寄生电容耦合到步线较有效,串扰发生更容易;

(3)信号回路尺寸与时钟频率及其谐波的波长相比拟,辐射更加显著;

(4)引起信号线路反射的阻抗不匹配问题。

二、总体概念及考虑

1. 五一五规则,即时钟频率到5MHz或脉冲上升时间小于5ns,则PCB板须采用多层板。

2. 不同电源平面不能重叠。

3. 公共阻抗耦合问题。

模型: